- 存储系统概述

- 存储系统的层次结构

-

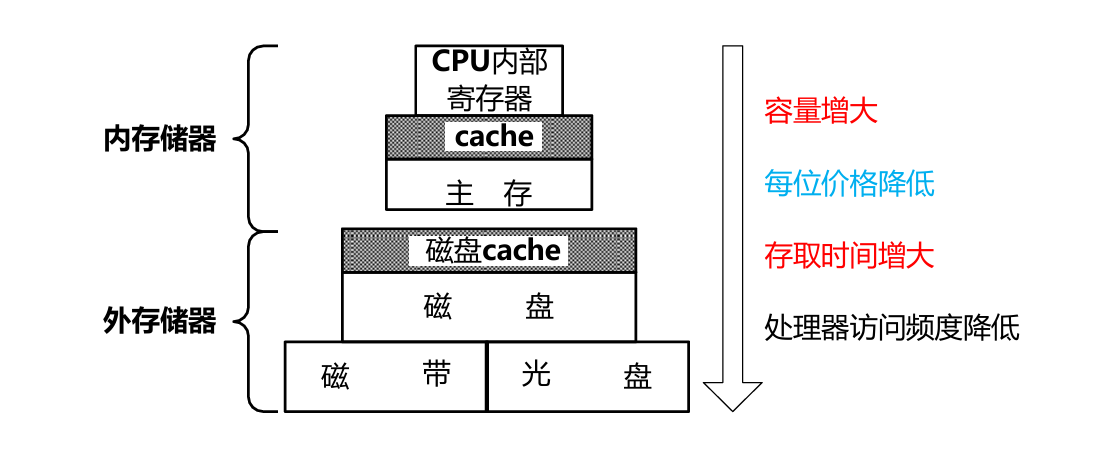

为了解决存储容量、存取速度和价格之间的矛盾,计算机中通常采用多级存储器体系结构,即使用高速缓冲存储器、主存储器和外存储器。CPU能直接访问的存储器称为内存储器,包括高速缓冲存储器和主存储器。CPU不能直接访问外存储器,外存储器的信息必须调入内存储器才能被CPU处理。

-

高速缓冲存储器-主存 层次:CPU的处理速度比主存的存取速度快。为弥补主存速度的不足,在主存和CPU之间增加一级高速缓冲存储器(Cache)。其特点是速度高而容量小。它所存放的是主存中部分内容的复制,是当前最有可能被CPU访问的信息。

-

从整体看,Cache-主存层次的存取速度接近于Cache的速度,而容量接近于主存的容量。Cache存储器全部由硬件调度,对程序员是透明的。

从整体看,主存-辅存层次具有接近于主存的速度和接近于辅存的容量。

-

- 存储器的分类

- 按存储介质分 • 半导体存储器:主要有MOS型存储器和双极型存储器两大类。 • 磁表面存储器:在金属或塑料基体上,涂覆一层磁性材料,用磁层存储信息,常见的有磁盘、磁带等。 • 光存储器:采用激光技术访问的存储器。

- 按存取方式分

• 随机存储器:任何存储单元的内容都能被随机存取,且存取时间和存储单元的物理位置无关。如半导体存储器。

• 顺序存储器:只能按某种顺序来存取,存取时间和存储单元的物理位置有关。如磁带存储器。

磁盘存储器既不像随机存储器那样能随机地访问任一个存储单元,也不像顺序存储器那样完全按顺序存取,而是介于两者之间。存取信息时,第一步指向整个存储器中的某个小区域(磁盘上的磁道);第二步在小区域内顺序检索,直至找到目的地后再进行读/写操作。其存取时间和信息的物理位置有一定关系。

-

按存储器的读写功能分 • 只读存储器(ROM):存储的内容固定不变,只能读出而不能写入。 • 随机读写存储器(RAM):既能读出又能写入。

-

按信息的可保存性分

• 易失性存储器:断电后信息即消失的存储器。 • 非易失性存储器:断电后仍能保存信息的存储器。 - 按在计算机系统中的作用分

• 根据存储器在计算机系统中所起的作用,可分为主存储器、辅助存储器、高速缓冲存储器、控制存储器(用于存放微程序,由ROM构成)。

- 存储器的编址和端模式

-

-

存储容量:存储器所包含的存储单元的总数称为存储容量。存储容量用字数或字节数表示。一个字节定义为8个二进制位,一个字包括2个或4个字节。

- 存取时间:从启动一次存储器操作到完成该操作所经历的时间。例如:读出时间是指从CPU向主存发出有效地址和读命令开始,直到将被选单元的内容读出为止所用的时间;写入时间是指从CPU向主存发出有效地址和写命令开始,直到信息写入被选中单元为止所用的时间。

- 存取周期:连续两次访问存储器操作之间所需要的最短时间。一般情况下,存取周期大于存取时间。这是因为对于任何一种存储器,在读写操作之后,总要有一段恢复内部状态的复原时间。

- 存储器带宽:又称数据传输率,指单位时间内存储器可读写的数据量,用位/秒或字节/秒度量。由存取周期和字长决定。

- 可靠性:用平均无故障时间来衡量。

- 其它参数:功耗、价格等。

-

- 存储系统的层次结构

-

静态随机存取存储器

目前广泛使用的半导体存储器是MOS型半导体存储器,可以分为静态MOS型存储器(Static RAM)和动态MOS型存储器(Dynamic RAM)

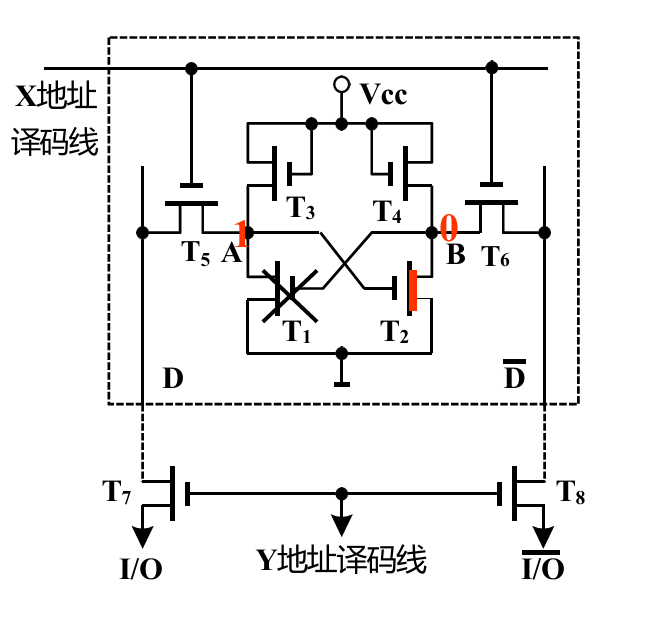

六管SRAM存储元的电路图$T_3、T_4$相当于负载电阻,$T_1、T_2$构成双稳态触发器。若$T_1$截止,A为高电平,使$T_2$导通,B为低电平,而B的低电平又使$T_1$更加截止;反之,若B为高电平,则A为低电平。

可见该电路有两个稳定状态,且A和B两点电位总是互反的。如果用A点高电平代表 “1”,A点低电平代表 “ 0”,该电路可存储一位二进制数。

$T_5、T_6、T_7和T_8$为控制管。如果某存储元被选中,X、Y地址译码线均处于高电平,使$T_5~T_8$导通,输入输出电路I/O和$\overline{I/O}$分别与A点和B点相连,A点和B点的电平状态就能输出到I/O和$\overline{I/O}$上,完成读操作。

写操作时,如果要写入“1”,在I/O线上输入高电位,在$\overline{I/O}$线上输入低电位,开启$T_5~T_8$四个MOS管把高、低电位分别加在A、B点,使$T_1$管截止,使$T_2$管导通,将“1”写入存储元。如果要写入“0”,在I/O线上输入低电位,在$\overline{I/O}$线上输入高电位,打开$T_5~T_8$,把低、高电位分别加在A、B点,使$T_1$管导通,$T_2$管截止,将“0” 写入存储元。

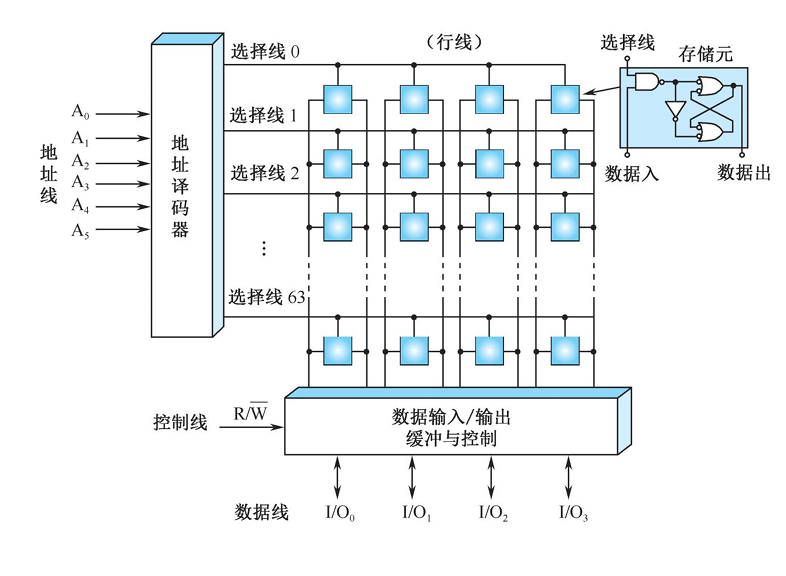

本例任何一个 SRAM,都有三组信号线与外部打交道: ①地址线,本例中有 6 条,即 $A_0、A_1、 A_2、 A_3、 A_4、 A_5$,它指定了存储器的容量是 $2^6$=64 个存储单元。 ②数据线,本例中有4 条,即 $I/O_0、 I/O_1、 I/O_2 、 I/O_3$,说明存储器的字长是 4 位,因此存储位元的总数是 64×4=256。 ③控制线, 本例中 $R/\overline{W}$ 控制线, 它指定了对存储器进行读( $R/\overline{W}$ 高电平), 还是进行写( $R/\overline{W}$低电平)。注意,读写操作不会同时发生。

-

SRAM存储器由存储体、地址译码电路、读写电路和控制电路组成。 * 存储体: 存储体是存储单元的集合。 * 地址译码器:CPU要选择某一存储单元,就在地址总线上输出该单元的地址信号给地址译码器,译码器把二进制代码表示的地址转换成电平信号,选中要访问的存储单元。 * 片选与读写控制电路:读写控制线用来控制芯片是进行读操作还是写操作;片选线用来决定该芯片是否被选中。

- SRAM读/写时序

- 存储器容量的扩充

- 存储器与CPU的连接

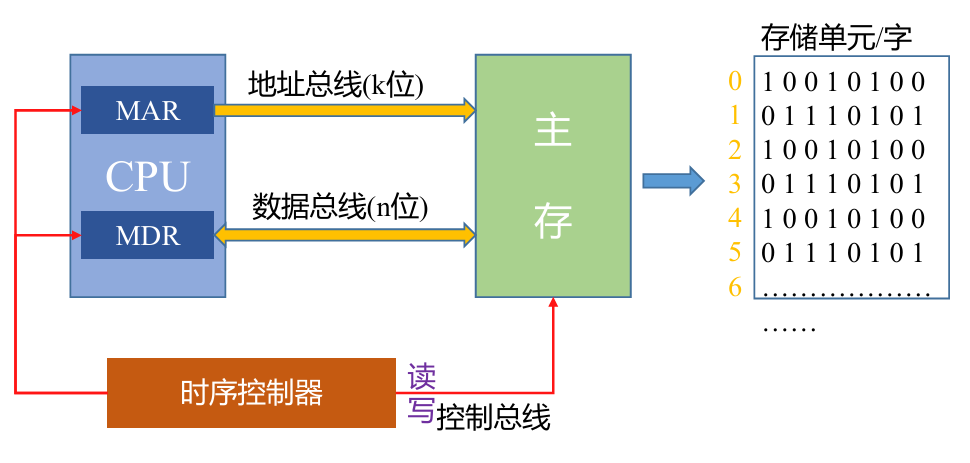

存储容量: 半导体存储芯片所能存储的二进制信息位数(单位bit)

可寻址最大范围: $2^k n$ (单位bit,1Byte=8bit)

RAM芯片通过地址线、数据线和控制线与外部连接。存储器同CPU的连接就是要完成地址线、数据线和控制线的连接。地址线是单向输入的,数据线是双向的,既可输入也可输出。单个芯片的存储容量往往不能满足要求,需要进行扩展。扩展的方法有:位扩展法、字扩展法、字位同时扩展法。

-

- 动态随机存取存储器

- 只读存储器

- 并行存储器

- cache存储器

- 虚拟存储器

- 奔腾系列机的虚存组织